Insights:

Cadence and TSMC advance AI and HPC chip design with AI-driven automation and IP.

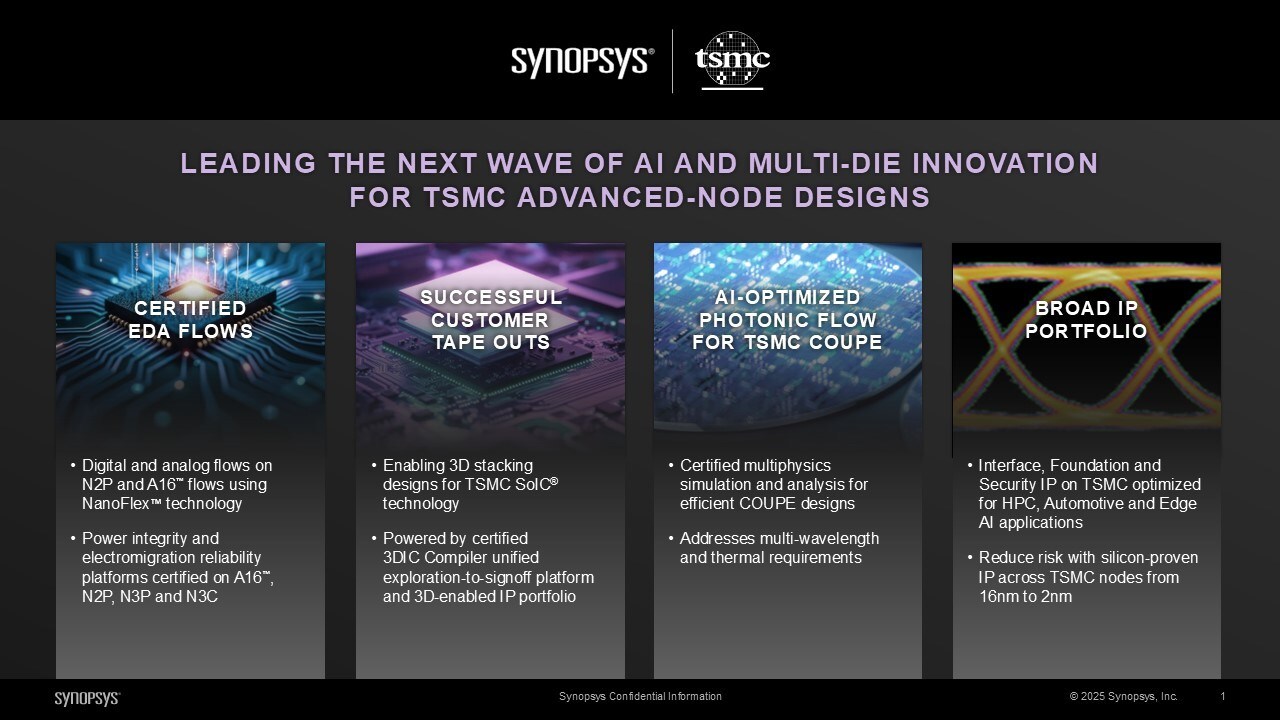

Support for TSMC’s latest process nodes including N3, N2, A16, and upcoming A14 PDK.

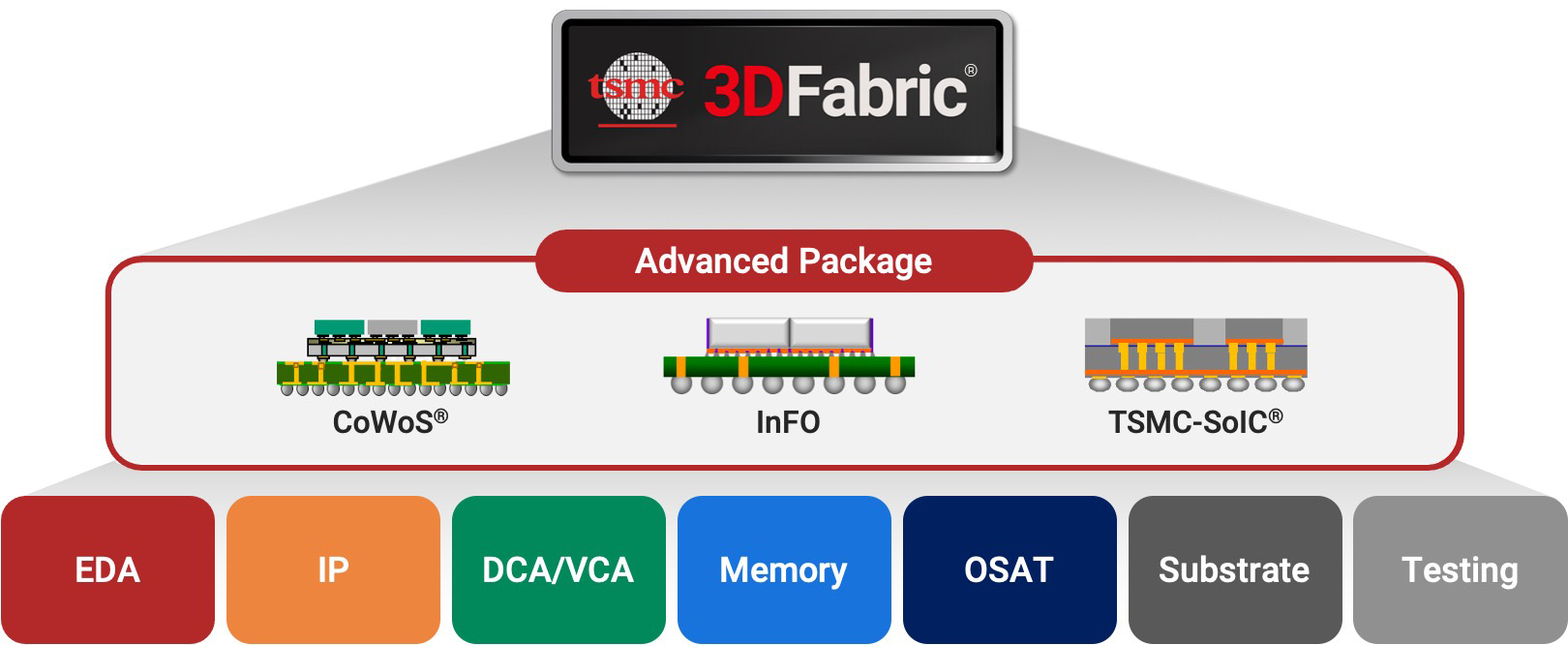

Enhanced 3D-IC design productivity enabled by Cadence solutions integrated with TSMC’s 3DFabric.

New silicon-proven IP such as HBM4, LPDDR6/5X, PCIe 7.0, and Universal Chiplet Interconnect for AI workloads.

Partnership accelerates design-to-silicon journey, boosting performance and energy efficiency for next-gen semiconductors.

Cadence Design Systems and TSMC continue to strengthen their partnership, delivering significant advancements in chip design automation and intellectual property (IP) to meet the demands of AI and high-performance computing (HPC) applications. Their collaboration encompasses support for the latest advanced process nodes including TSMC’s N3, N2, A16™, and upcoming A14 process technologies, leveraging AI-driven Electronic Design Automation (EDA) tools to optimize power, performance, and area.

Cadence’s AI-powered design flows and tools like Innovus Implementation System, Cerebrus Intelligent Chip Explorer, and Clarity 3D Solver enhance productivity in complex chip and 3D-IC designs. Notably, integration with TSMC’s 3DFabric packaging technology and Compact Universal Photonic Engine facilitates system-level simulation and thermal management innovations.

The two companies have also introduced cutting-edge silicon-proven IP on TSMC’s N3P node, including high-speed memory interfaces such as HBM4 and LPDDR6/5X, PCI Express 7.0 IP, and Universal Chiplet Interconnect (UCIe) IP. These developments are critical for addressing AI infrastructure challenges like memory bandwidth and energy-efficient scalability. Overall, this partnership empowers semiconductor customers to accelerate innovation and deploy advanced AI chips faster and more efficiently.

Note: All images and Products & Trademarks mentioned in this article are copyrighted to companies:

Cadence Design Systems, TSMC, PCI-SIG, UCIe Consortium