2025 OCP Global Summit

San Jose, California

October 13–16, 2025

Registration: https://www.opencompute.org/summit/global-summit/registration

Insights:

- The 2025 OCP Global Summit focuses on driving AI data center innovation through openness, efficiency, sustainability, and scalability.

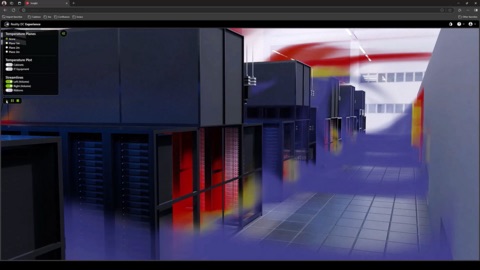

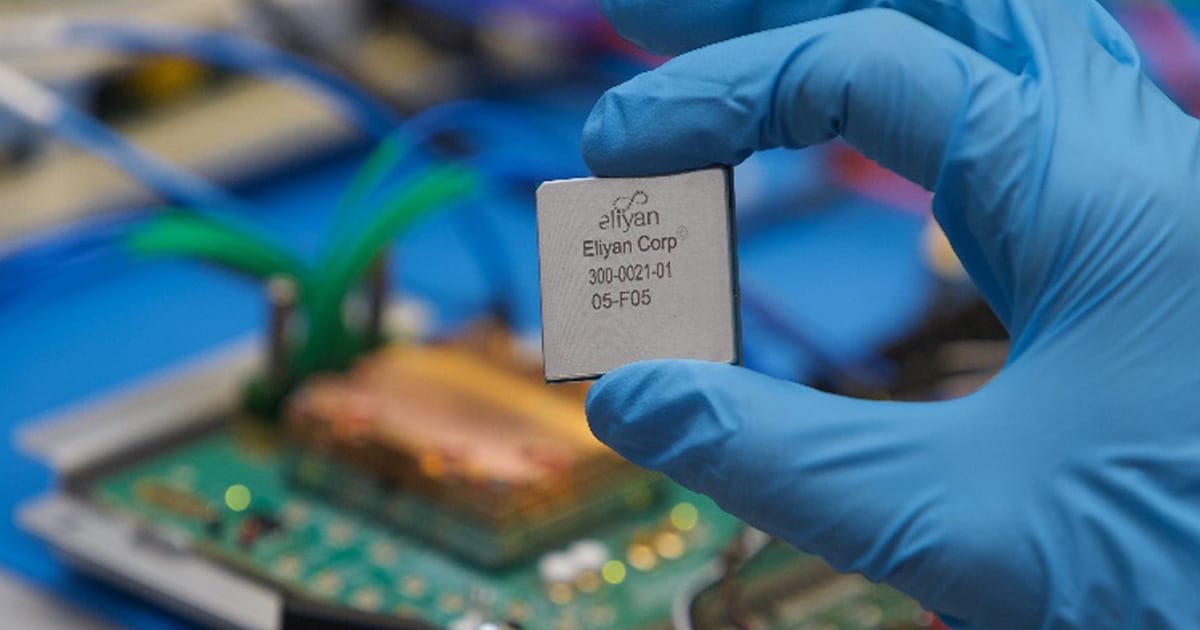

- AI workloads require rethinking data center infrastructure including chiplet technology, cooling, power, networking, and systems management.

- Edge computing for AI inference demands smaller, high-performance equipment and ultra-low latency optical networks.

- Sustainability, particularly reducing power, water consumption, and carbon emissions, is a critical priority for future data center design.

- The OCP AI HW/SW Co-Design group’s promotion to an official OCP Server Project signifies growing maturity and industry commitment.

The 2025 Open Compute Project (OCP) Global Summit, themed “Leading the Future of AI,” highlights ongoing collaborations within the OCP community aimed at shaping the future of AI data centers. As AI rapidly transforms industries and economies, there is unprecedented demand for scalable, efficient, and sustainable data center infrastructure. The summit brings together global leaders to share innovations, standardize technologies, and foster partnerships that support this AI-driven evolution.

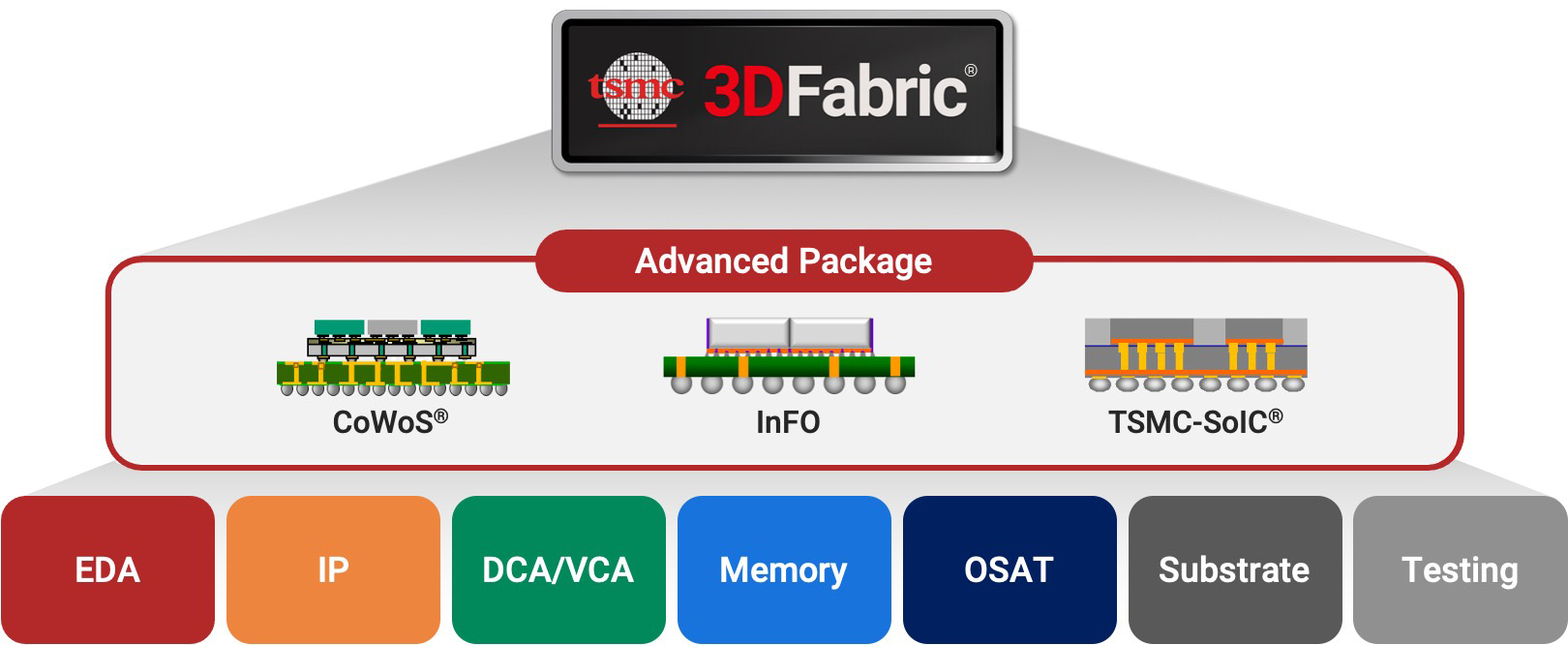

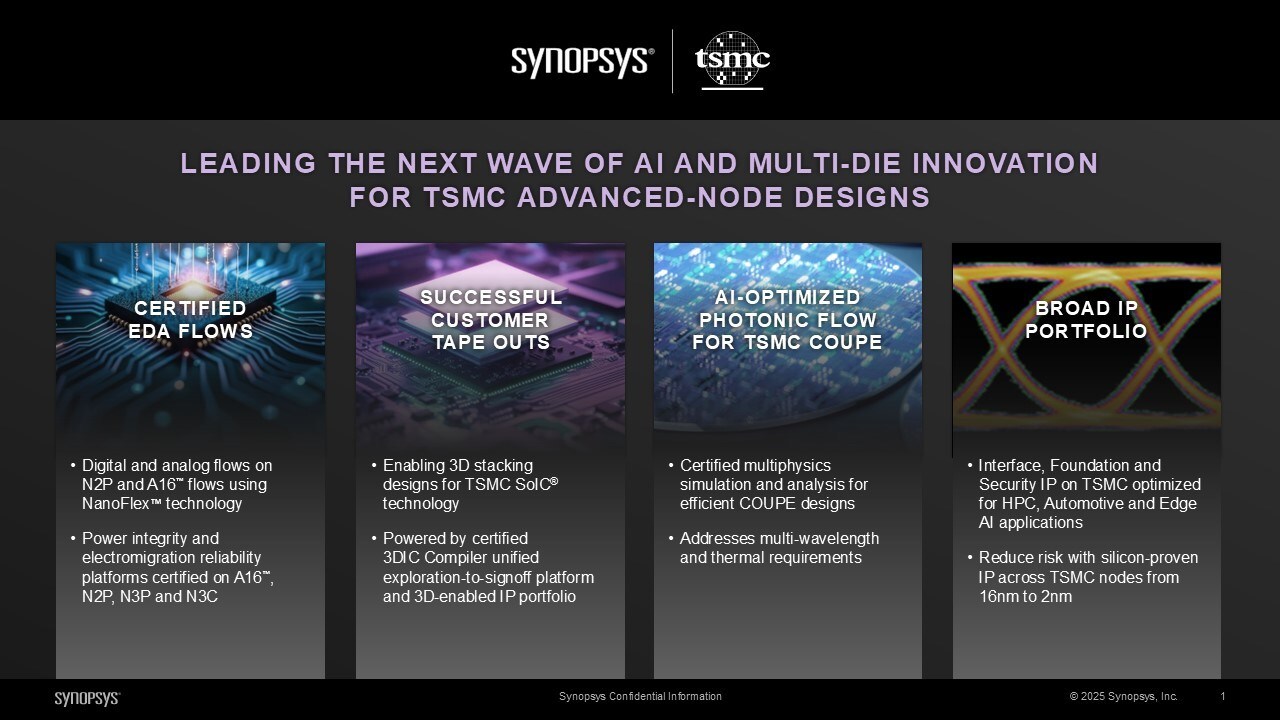

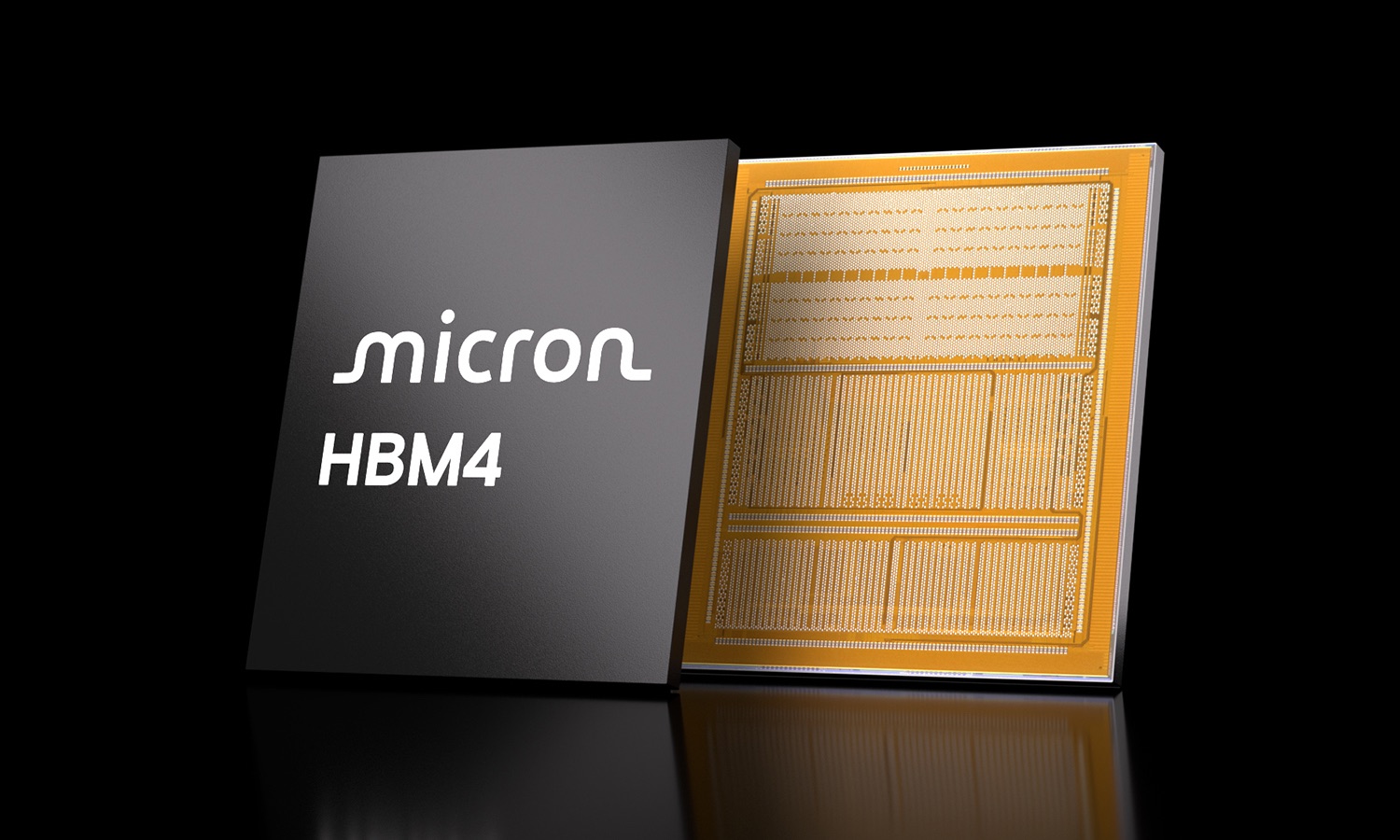

Key advancements include breakthroughs in chiplet technologies, advanced packaging, and critical subsystems like cooling, power distribution, networking, and server architectures. The shift toward edge computing for AI inference calls for compact yet powerful computational resources combined with high-speed, low-latency optical communication networks. Sustainability remains a major focus, with ongoing efforts to reduce energy consumption, water usage, and carbon footprint within data center facilities.

Additionally, the elevation of the AI Hardware/Software Co-Design group from a Future Technologies Initiative to an official OCP Server Project underlines the growing importance of integrated AI infrastructure development. Hosted by Rackspace and originally founded by Meta (formerly Facebook), the OCP community continues to lead in openness and innovation, paving the way for next-generation AI data centers worldwide.

Note: All images and Products & Trademarks mentioned in this article are copyrighted to companies:

Meta, Rackspace